Abstraction

하드웨어, 소프트웨어, 컴퓨터를 포함한 모든 공학 도구나 물건은 Interface와 Implementation으로 구성되어 있다.

Selective Ignorance의 특징을 지닌다. 따라서 Implementation을 몰라도 Interface만 알면 사용이 가능하다.

- Interface = 사용법 = service = abstraction

- Implementation

- 구현, 설계, 구조, 동작

- Interface을 구현한 것으로, interface을 제공한다.

예시 : CS에서의 Interface

Machine-level Programming

- Interface : machine instruction

- Implementation : machine(CPU)

High-level programming

- Interface : programming language

- Implementation : complier, interpreter

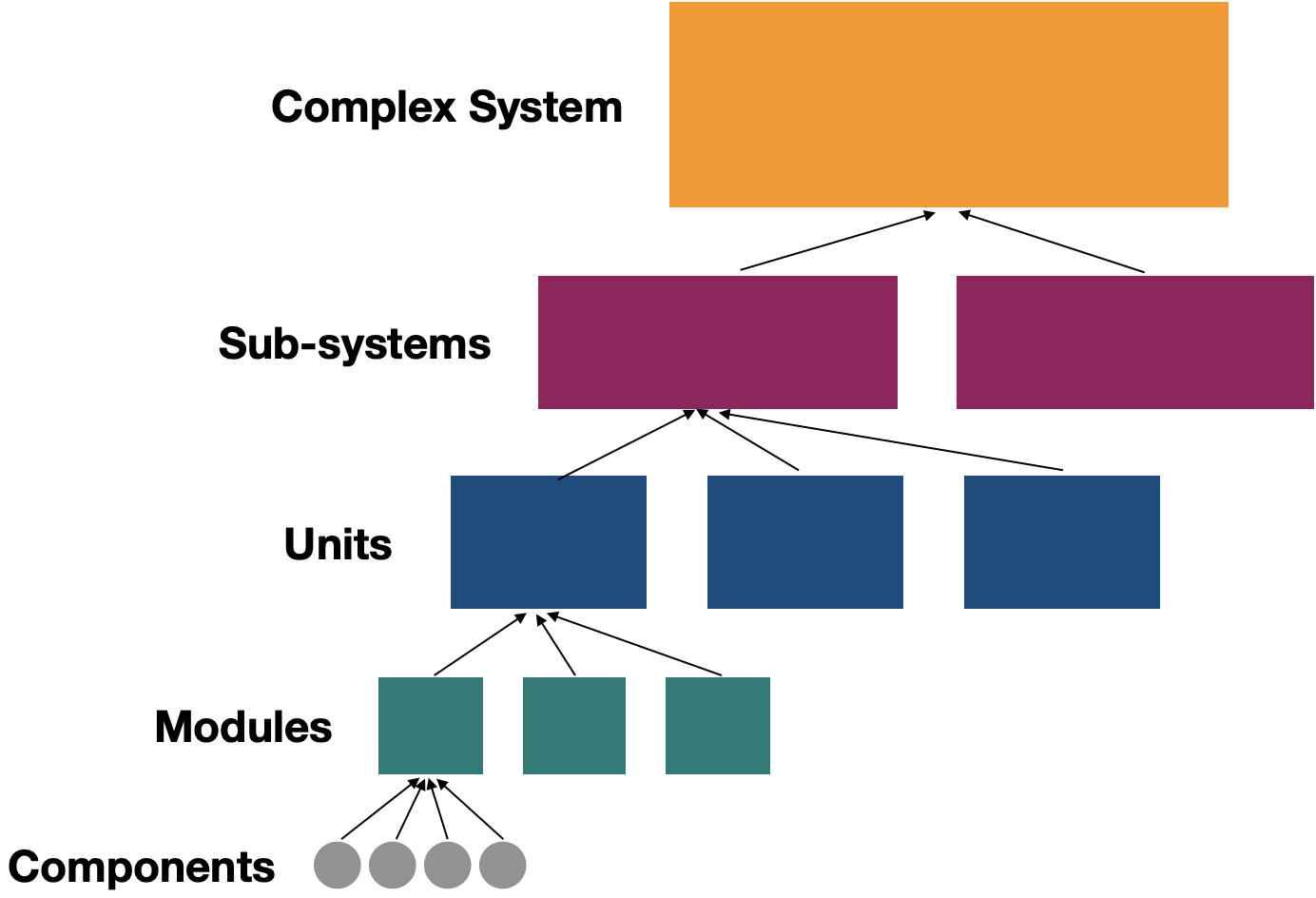

Primitive-Composition-Abstraction

= Hierarchical Abstraction

Digital logic design의 fundamental paradigm이다.

복잡한 공학 제품을 만들기 위해서는 Hierarchical abstraction building이 필수적이다.

작은 부품들로 복잡한 모듈을 만들고, 이들로 더 복잡한 것들을 만들어나가면서 최종적인 product를 만들어 가는 것이다.

모든 공학이 이런식이고 차이점은 primitives가 다를 뿐이다.

Hardware Design

Hardware design이란 hierarchical하게 점점 더 복잡한 abstraction을 만들어가는 과정이다.

- Fundamental paradigm

- Primitive

- AND, OR, NOT

- Digital logic design에서 primitive는 항상 AND, OR, NOT이다.

- Composition

- primitive을 이용해서 더 복잡한 function unit(FU)을 만들어간다.

- Abstraction

- Implementation을 몰라도 주어진 interface로 FU을 사용할 수 있다.

- FU는 primitive가 되고, 다시 이 paradigm을 통해 점점 복잡한 abstraction을 만들 수 있다.

- Primitive

Combinational Logic의 Hierarchical Abstraction 예시

: ALU design

간단하게 Hierarchical abstraction 구조를 나타내면 다음과 같다.

1-bit Full Adder

먼저, 1-bit full adder를 살펴보자. Input과 Output, 기능은 다음과 같다.

- Input : 더할 2개의 bits, carry(from right)

- Output : sum, carry(to left)

- Primitives : AND, OR, NOT

- 기능 : 오른쪽에서 넘어온 carry와 두 개의 bit을 더해서, sum을 산출하고 왼쪽으로 carray을 넘긴다.

Primitive란 사용 가능한 재료이다.

1-bit full adder의 interface와 implementation은 아래와 같다.

아래에서 XOR는 ADD, OR, NOT을 이용하여 구현 가능하여여, 그 implementation만 나타낸 것이다.

Multiplexor

Muliplexor (MUX)는 Data selector로, 들어오는 중 일부를 선택해서 output으로 내보낸다.

2-to-1 MUX

Input의 2개 신호 중 1개를 선택해서 output으로 내보낸다.

- Input : 2개의 bit, Select signal

- Output : 선택된 1개의 bit

- Primitives : AND, OR, NOT, XOR

4-to-1 MUX

Input으로 들어온 4개의 신호 중 1개를 선택해서 output으로 내보낸다.

- Input : 4개의 bit, Select signal

- Output : 선택된 1개의 bit

- Primitives : AND, OR, NOT, XOR

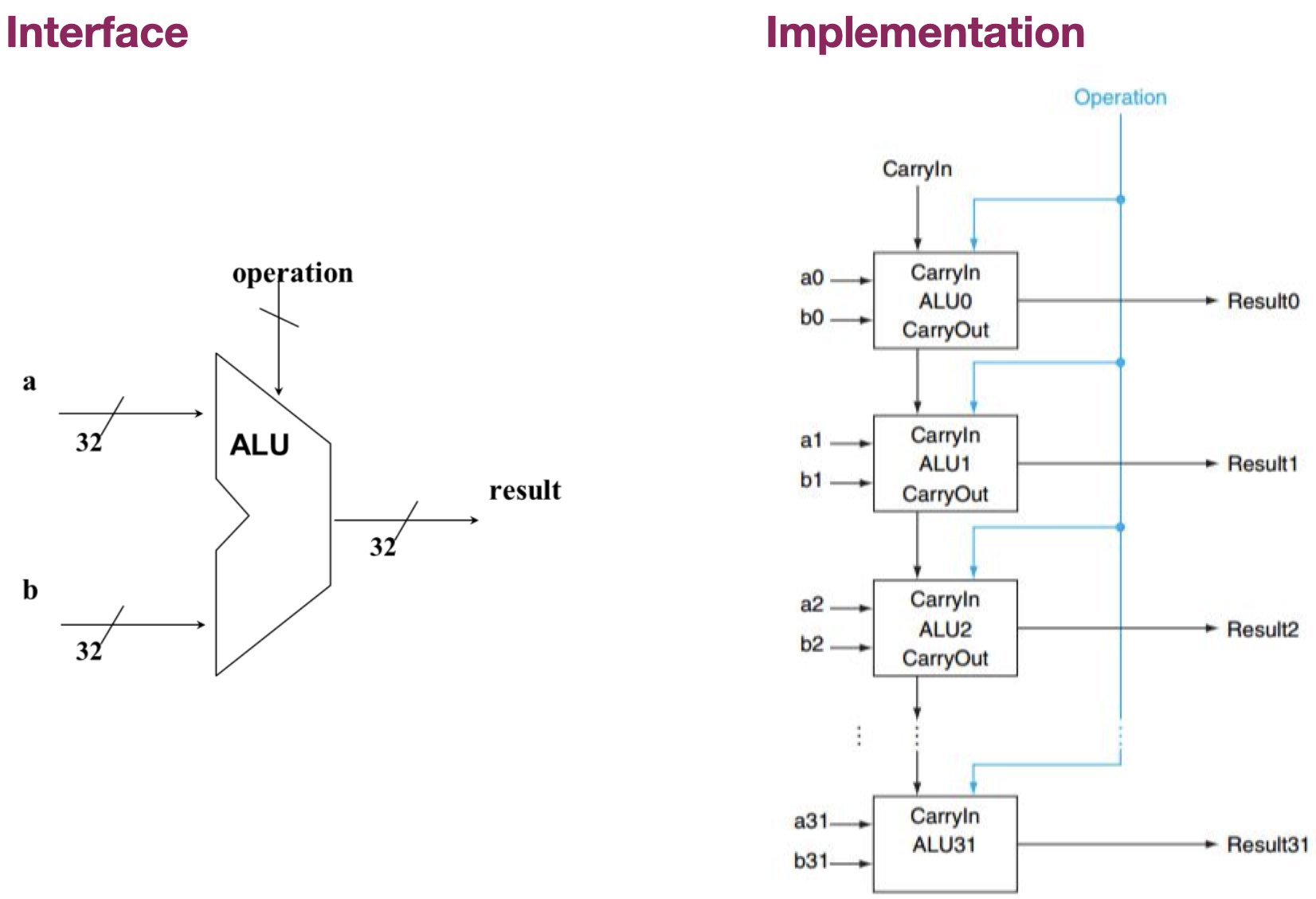

1-bit ALU, 32-bit ALU

ALU란 Arithmetic Logic Unit으로 4칙연산을 담당한다.

편의상 1-bit ALU 대신에 1-bit Adder을 표현하였다.

덧셈이 가능하면 뺄셈이 가능해지고, 이를 여러번 반복하면 곱셈이 가능하지고 곱셈의 역으로 나눗셈이 가능해지기 때문이다.

1-bit ALU

- Input : 연산할 2개의 bits, carry, 수행할 operation의 종류

- Output : result, carray

- Primitives : AND, OR, NOT, XOR, MUX

32-bit ALU

1-bit ALU을 다시 이용해서 32-bit ALU을 나타내면 아래와 같다.

- Arithmetic : add, substract, multiply, divide

- Logical : bitwise AND, OR, NOT

CPU

32-bit ALU에서 hierarchical abstraction을 통해서 CPU을 만들 수 있다.

CPU의 구성은 다음과 같다.

- ALU

- Arithmetic and logic unit

- Add, substract, multiply, devide, AND, OR, NOT

- Combinational logic

- Register

- CPU 안에 임시로 데이터를 저장하는 장소(임시 데이터를 저장한다.)

- Sequential logic

- PC

- Program counter

- 다음 실행시킬 instruction의 주소를 저장한다.

- IR : Instruction register

- Control logic

Sequential Logic의 Hierarchical Abstraction의 예시

: Register, Memory

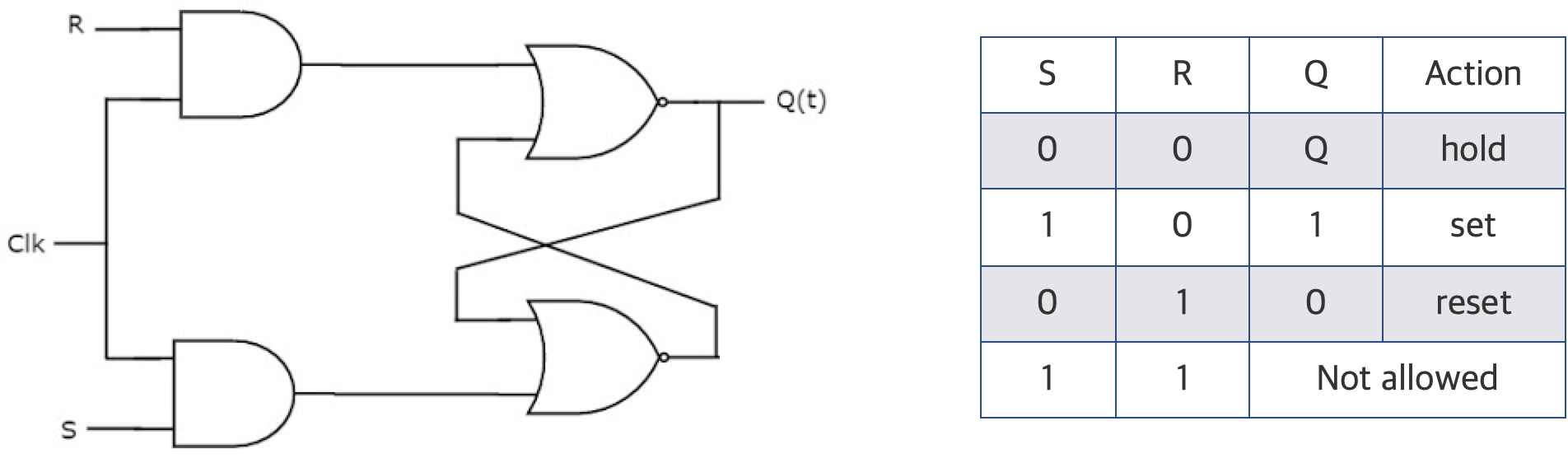

SR Flip-Flop

SR flip-flop은 Memory의 기능을 수행한다.

Abstraction과 기능의 동작은 다음과 같다.

1-bit Storage

SR flip-flop에 주변부를 붙여서 만들 수 있다.

Abstraction은 다음과 같다.

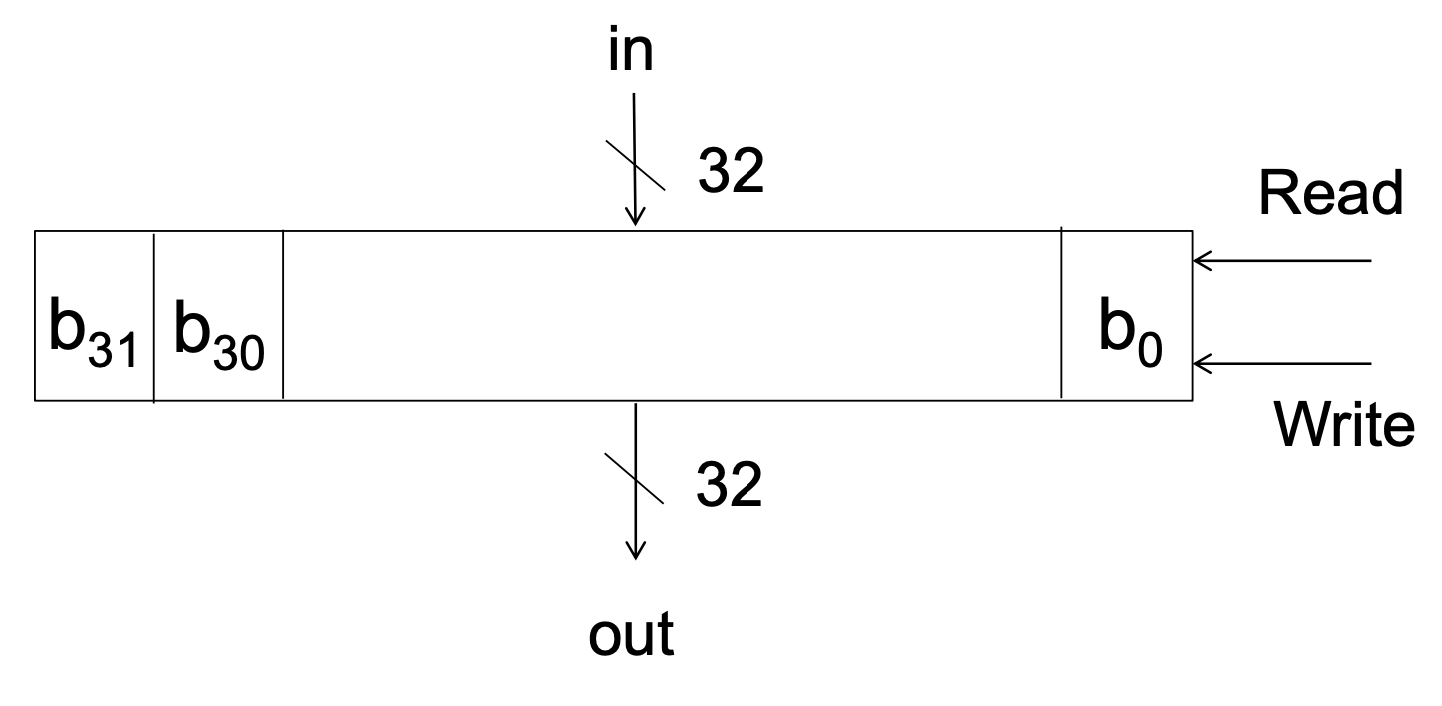

32-bit Storage

1-bit storage을 병행으로 연결하면 만들 수 있다.

모든 비트가 한번에 쓰이면 속도가 높아진다.

따라서 1-bit storage들을 parallel하게 연결한다.

레지스터는 프로세서에서의 32-bit storage이므로 이 자체로 레지스터라고 할 수 있다.

아래는 $b_{31} , b_{30} ...$ 등 자세한 내용이 나와있기 때문에 implementation이라 볼 수도 있다.

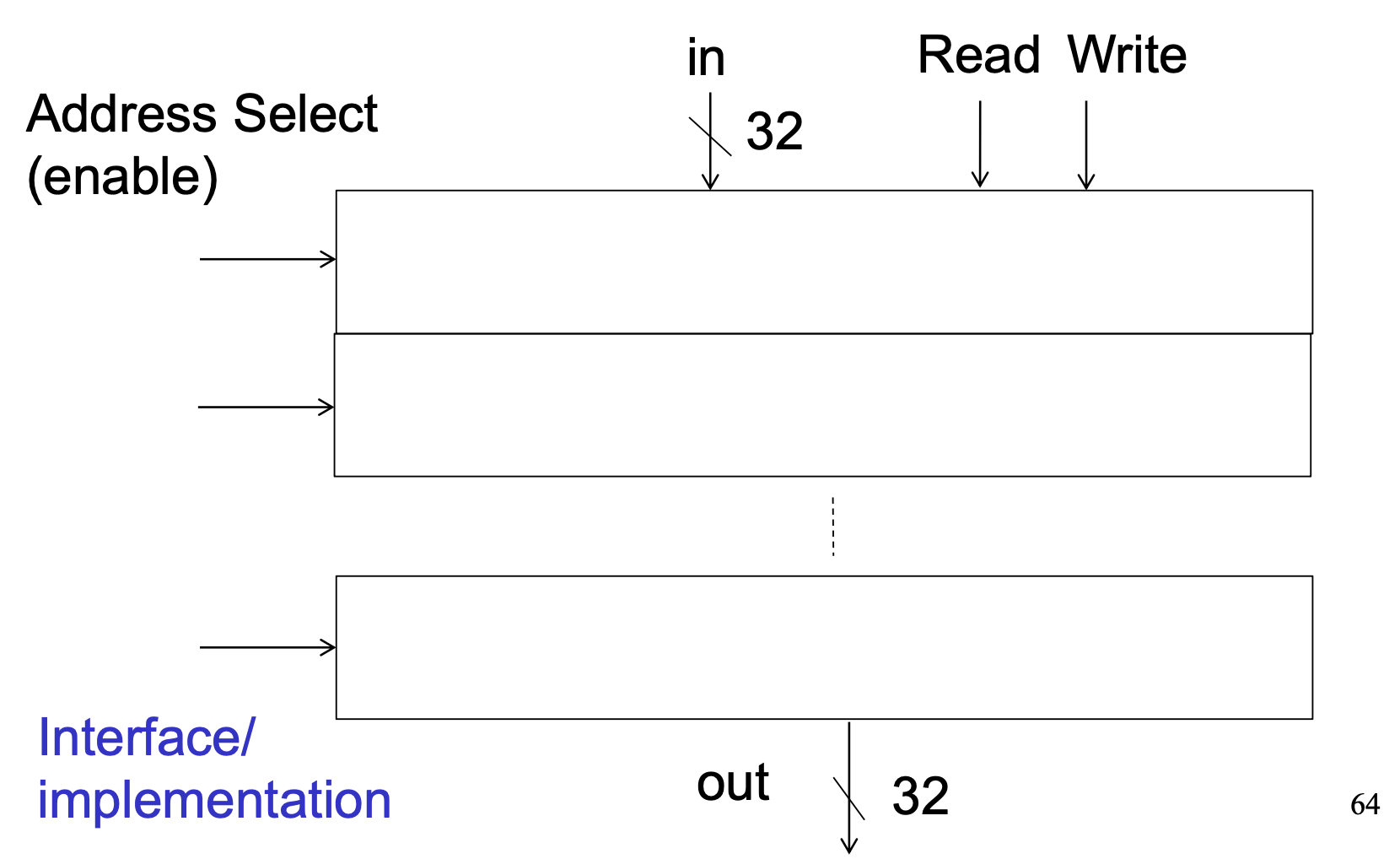

Main Memory

32-bit storage을 위아래로 여러개 포개놓으면 32-bit computer에서의 main memory가 된다.

이 때 CPU가 어느 storage에 저장할 것인지 결정해야 하는데 이 때 address라는 개념을 사용한다.

이를 위해 메모리가 있으면 반드시 address와 decoder가 존재하게 된다.

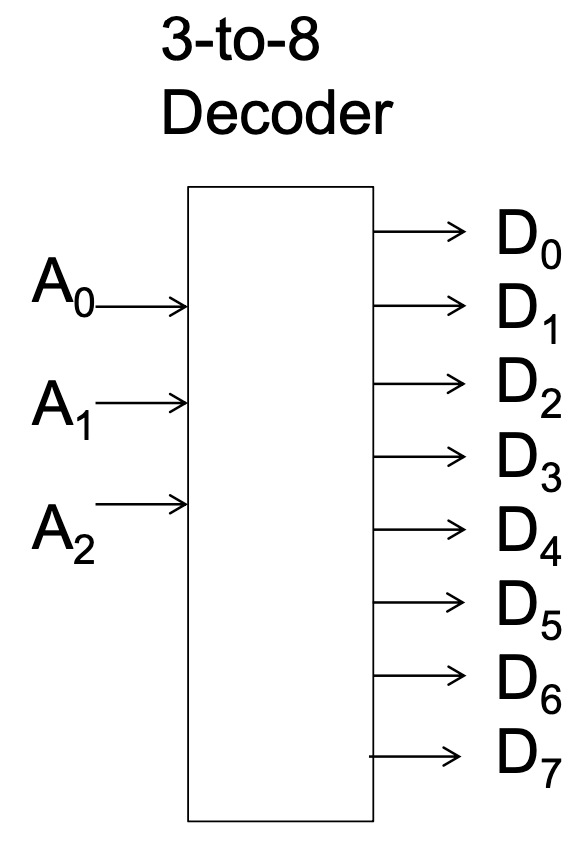

참고 : Decoder

Decoder는 사용하고 싶은 위치만 enable한 상태로 만들어 주는 combinational logic이다.

만약 main memory가 32-bit storage을 8개 붙여놓은 상태라면 3-to-8 decoder을 사용하면 된다.

8개의 위치를 선택하기 위해서는 3개의 bit만 사용하면 되기 때문인데,

3-to-8 decoder은 3개의 bit을 이용해서 8개 중 1의 결과만 enable한 상태로 만든다.

'Computer Science > Computer Architecture' 카테고리의 다른 글

| Data : type, storage, and C's data type (0) | 2021.03.17 |

|---|---|

| Abstraction과 Software Design (0) | 2021.03.14 |

| Transistor와 반도체 제조 공정 (0) | 2021.03.14 |

| Digital Logic : Combinational Logic, Sequential Logic (0) | 2021.03.13 |

| 컴퓨터의 탄생과 George Boole (0) | 2021.03.13 |

댓글