Multilevel Caches

배경

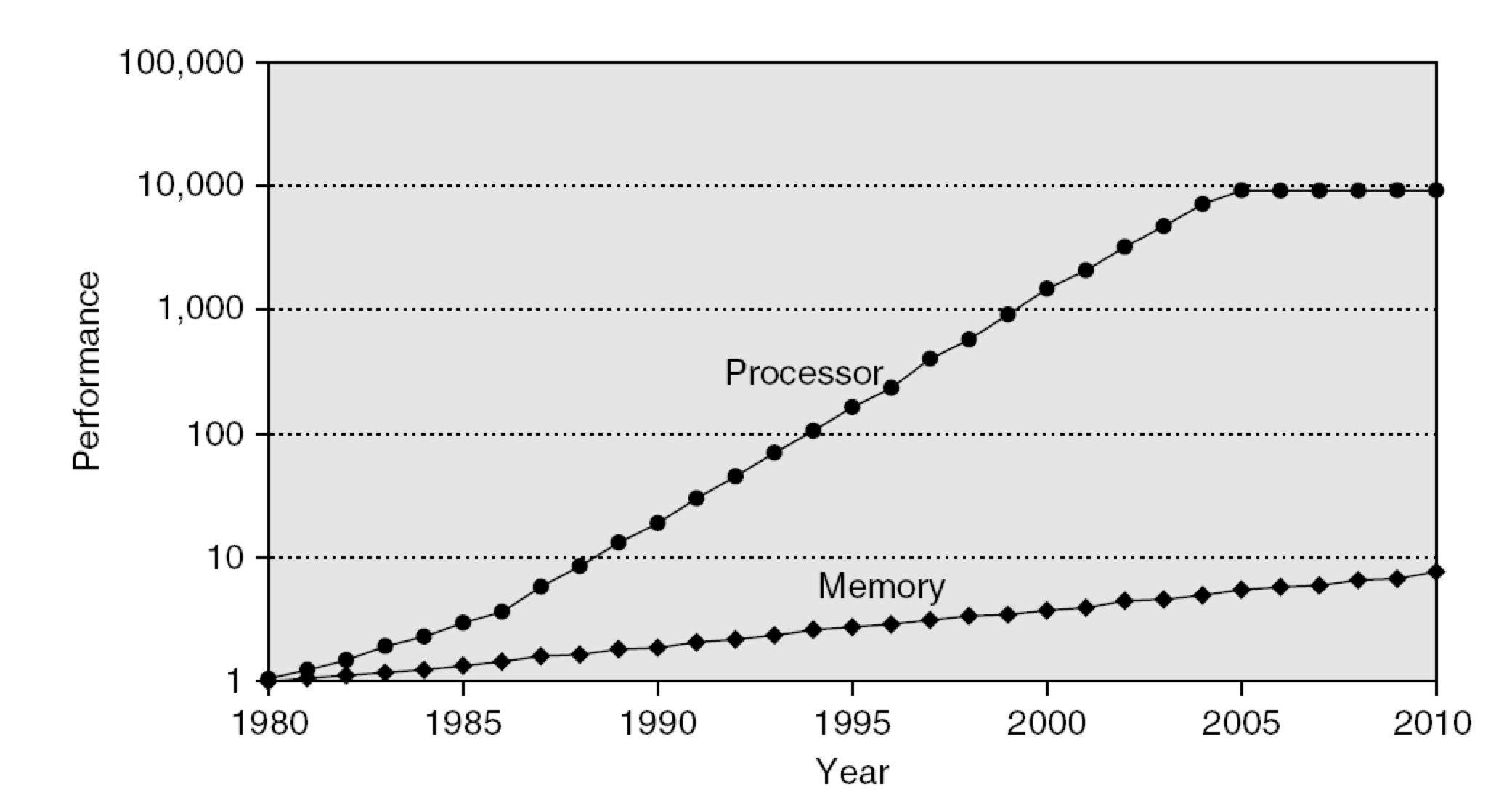

RISC architecture의 등장으로 processor의 성능이 exponential하게 증가하였다.

그러나 메모리의 속도는 크게 증가하지는 않았으며, 그에 따라서 CPU입장에서의 메모리는 속도가 점점 느려져갔다.

이를 해결하기 위해서 cache memory가 등장하였다.

그러나 차이는 점점 심해졌고, cache를 이용해도 극복 불가능하게 되었다.

Cache memory도 CPU의 속도를 따라가지 못하게 된 것이다.

Multilevel Caches (Two-Level)

메모리 속도와 CPU의 속도 간극을 해결하기 위해서 cache memory와 processor 사이에 하나의 cache를 더 추가한 것이다.

Cache가 2개 사용되었다 해서 2-level cache라고 한다.(layer가 2level)

L2 cache의 내용을 L1 cache로 caching하여 사용한다.

L1에서 miss가 나면 L2에서 가져오고, L2에서 miss가 나면 main memory에서 가져온다.

L1과 L2 모두 processor chip 안에 존재한다.

이에 따라 hit time이 빨라졌고, L1에서 hit이 나면 바로 가져다 쓸 수 있을 정도가 되었다.

Hit time 개선으로 인해서 cct도 개선되었다.

L1 cache는 L2보다 작고 훨씬 빠르다.

L2 cache는 L1에 비해서는 크고 느리지만, main memory보다는 훨씬 빠른 속도이다.

고가의 시스템은 L1, L2 뿐만 아니라 L3 까지 사용하기도 한다.

Split vs. Unified

Strutural hazard를 피하기 위해서 CPU가 직접 access 하는 메모리만 split으로 구현하면 된다.

이외의 다른 메모리는 data와 instruction 중에서 더 많이 쓰는 부분을 더 많이 할당함으로써 성능을 개선시키기위해서 unified로 구성한다.

따라서 multi-level cache에서는 L1 cache만 split 되어있다.

L1 vs L2 Cache

Cache memory의 크기가 커지면 hit time은 증가한다.

L1은 CPU가 직접 access하기 때문에 크기를 작게해서 속도를 빠르게 해야 한다.

그래야 hit time이 감소하고, CPU가 빠른 clock으로 동작이 가능하다.

그러나 L2는 CPU가 직접 access 하지 않기 때문에 CPU의 clock speed와 직접적인 연관이 없다.

따라서 L2는 충분히 커져도 된다.

L2가 커지면 L1에서 miss 나는 것을 더 받쳐줄 수 있다.

Performance

Multilevel Cache를 사용하는 이유

Hit time이 빨라지기 때문에 multilevel cache를 사용한다.

Hit time은 cct를 결정하기 때문에 결국 cct가 개선된다.

또한 average memory access time이 더 작아지게 된다.

Average Memory Access Time (AMAT)

In 1-level Cache

average memory access time

= hit time + miss rate x miss penalty

In 2-level Cache

average memory access time

= L1 hit time + L1 miss rate x (L2 hit time + L2 miss rate x L2 miss penalty)

예시

1-level cache에서 CPU가 100번 cache access 하면 그 중 5번은 cache miss가 발생한다.

따라서 average access time = 10 + 0.05 x 100 = 15 cyces 이 된다.

반면 2-level cache에서는 CPU가 100번 L1 access를 하면, 그 중 10번은 miss가 난다.

L1에서 miss가 나면 L2에 access 하게 되고, 10번 중 5번은 miss가 나게 된다.

따라서 average access time = 1 + 0.1 x ( 10 + 0.5 x 100 ) = 7 cycles 가 된다.

이 때 10번 중 5번 꼴로 L2에서 miss가 나게 되므로 L2에서의 miss rate는 0.5가 된다.

Miss Rate

1-level cache나 2-level cache나 main memory에 가는 확률 자체는 비슷하다.

1-level에서의 cache와 2-level에서의 L2 cache 크기 자체는 동일하기 때문이다.

'Computer Science > Computer Architecture' 카테고리의 다른 글

| 5. Cache - Virtual Memory Interaction (0) | 2021.06.13 |

|---|---|

| 5. Virtual Memory (0) | 2021.06.13 |

| 5. Write Strategy (0) | 2021.06.11 |

| 5. Set-Associative Mapping (1) | 2021.06.11 |

| 5. Direct Mapping (0) | 2021.06.11 |

댓글