Instruction Set

Dependency

Dependency(독점성)을 위해서 다른 프로세서는 다른 insturction set을 사용한다.

즉, 응용프로그램이 다른 프로세서로 넘어가기 힘들게 하여 고객을 뺏기지 않게 하기 위함이다.

그러나 기본적으로 오늘날의 컴퓨터는 모두 RISC style로, 32-bit 구조를 가지고 있다.

HW-SW interaction

프로세서는 응용프로그램을 돌리기 위한 것이다.

때문에 프로세서 designer들은 어떻게하면 벤치마크를 빠르게 돌릴 수 있는가를 고민한다.

이를 HW-SW interaction이라 한다.

CISC v.s. RISC

- CISC

- 하나의 instruction이 여러 기능을 담당한다.

- 메모리가 비쌌던 시절에 프로그램의 크기를 최대한 줄이는데 효율적이었다.

- IC는 줄어들지만, CPI와 cct는 크게 증가하기 때문에 오늘날에는 비효율적이다.

- RISC

- simple instruction만 담고 있고, complex한 것은 여러 instruction을 실행해서 구현한다.

- Load-Store architecture : load/store을 통해서만 메모리에 접근한다.

- 비록 IC는 증가하지만, CPI와 cct는 감소하기 때문에 성능을 높이는데 유리하다.

- 파이프라인을 통해서 IC을 줄인다.

- 메모리가 비교적 저렴한 오늘날에는 모두 RISC를 사용한다.

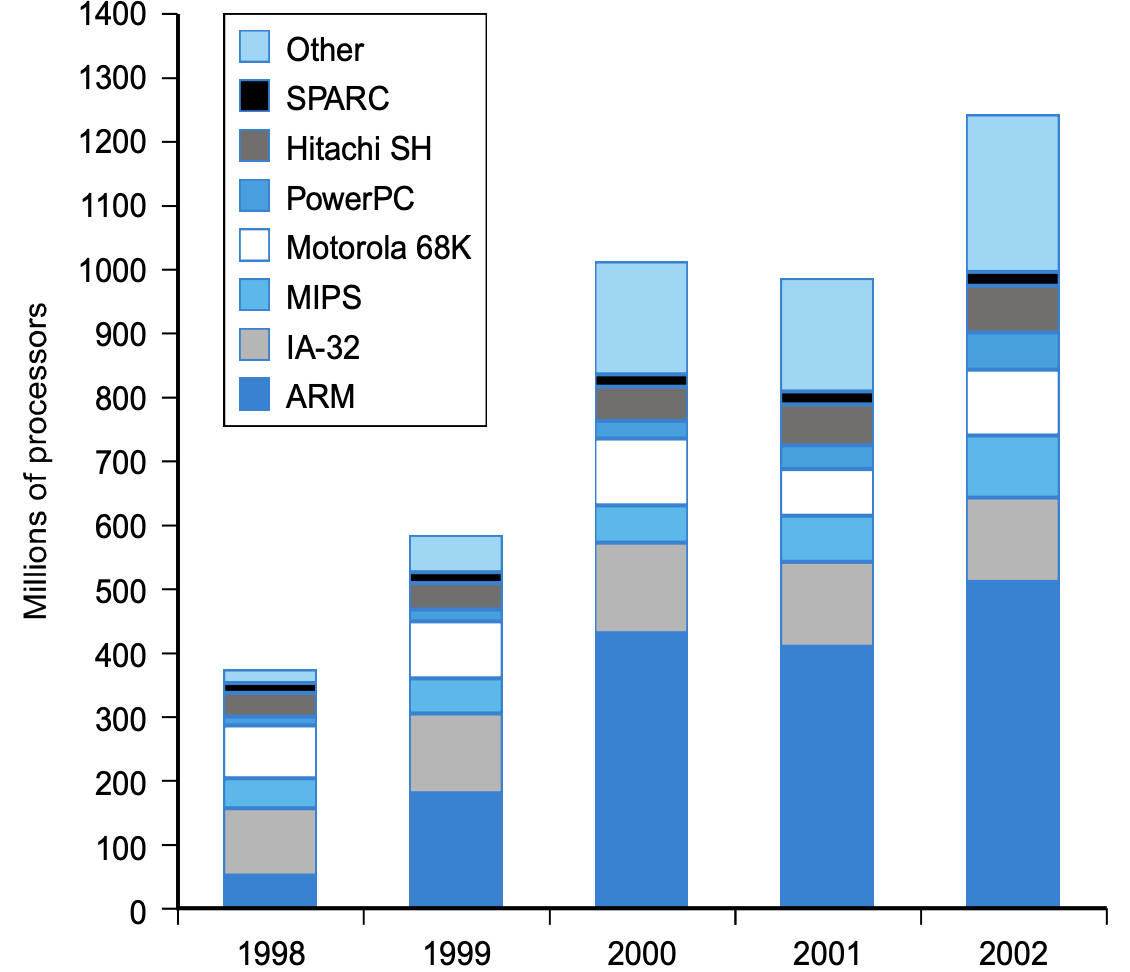

다양한 ISA

ARM, MIPS, IA-32 등 다양한 종류의 ISA가 존재한다.

IA-32는 high performance processor이다.

ARM은 반도체 제조시설(FAB)없이 설계만해서 판매한다.

사용하는 업체에서 반도체를 직접 생산해서 사용한다.

대부분 임베디드 시스템과 모바일 시장에서 차지하고 있으며, 때문에 점유율은 크지만 단가는 낮다.

임베디드 시스템은 성능은 높지만, 단가와 power consumption은 낮은 프로세서를 요구한다.

MIPS Instruction Set

대표적인 RISC instruction set이다.

임베디드 시장에서 큰 점유율을 차지하고 있다.

RISC style의 단순하고 전형적인 예이기 때문에 요즘의 ISA을 학습하기에 적합하다.

Format and Addressing Mode

MIPS는 3개의 format과 5개의 addressing mode를 사용한다.

- Format

- instruction의 구조

- instruction에서 몇개의 operand을 사용할 것인가

- I-format, R-format, J-format

- Addressing mode

- instruction에서 어떤 operand를 어떻게 사용할 것인가

- Immediate addressing, Register addressing, Base addressing, PC-relative addressing, Pseudodirect addressing

MIPS Insturction의 종류

- ALU instruction

- I-format, R-format

- Immediate addressing, Register addressing

- Data transfer instruction

- I-format

- Base addressing

- Branch instruction

- R-format, I-format, J-format

- PC-relative addressing, Psudodirect addressing

Register Operand

MIPS는 32개의 register을 가지고, 각 레지스터는 32bit이다.(R0-R31)

레지스터는 프로그램 실행을 위한 데이터나 실행 도중 발생하는 데이터를 저장한다.

어느 레지스터에 어떤 데이터를 저장할지는 일반적으로 compiler나 assembly programming에서는 assembly programmer가 결정한다.

레지스터가 32개이므로, 레지스터를 구분하기 위해서는 5개의 bit만 필요하다.

Register 개수

레지스터의 개수가 32개인 것이 제일 적합하다.

레지스터의 개수는 opreand의 길이를 결정한다.

때문에 더 많은 레지스터는 instruction에서 다른 부분을 위해서 사용할 bit의 수가 줄어든다.

또한, 레지스터를 적게할 수록 register data에 접근하는 것이 더 빠르다.

레지스터를 구분할 때 적은 것에서 찾는 것이 더 수월하기 때문이다.

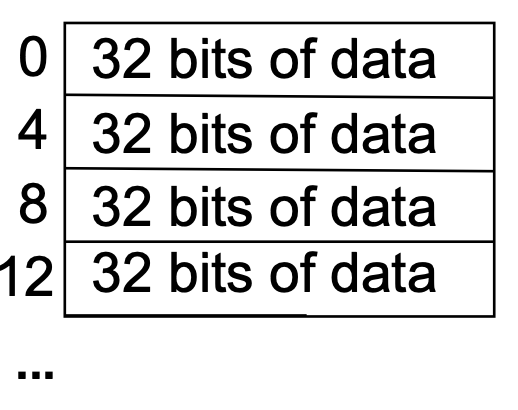

Memory Organization

메모리 구조에는 Byte addressing을 사용한다.

즉, 주소 1개당 1byte의 데이터를 저장한다.

단 데이터는 주로 word로 이루어지므로, 32bit의 구조를 맞추기 위해 4개를 묶어서 배열한다.

또한 word는 aligned되어 있어서 word들은 4의 배수를 시작 주소로 가지며 시작 주소의 끝 2bit는 항상 00이다.

word = 4byte(32bit)

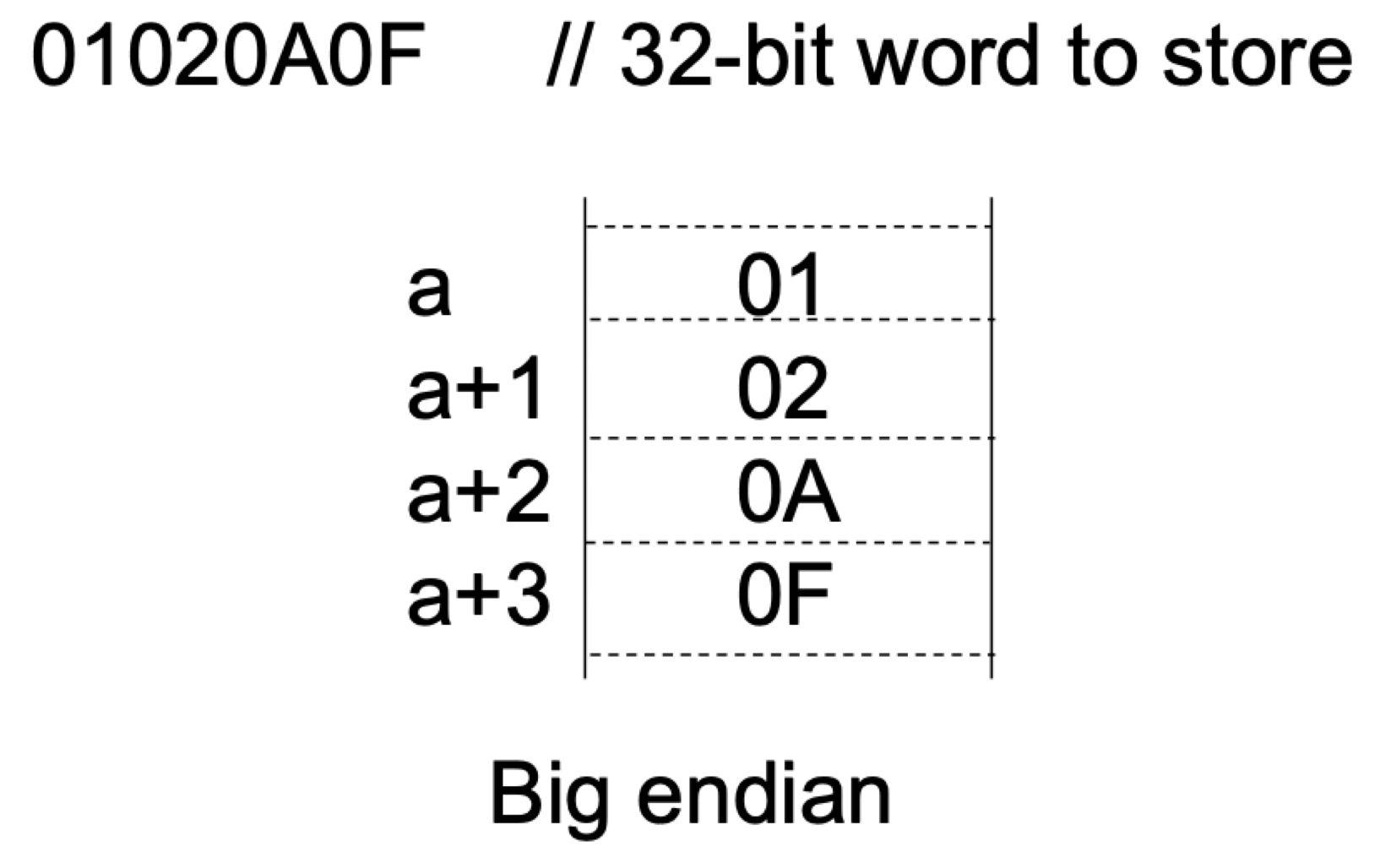

또한 MIPS는 big-endian을 사용한다.

word의 주소가 작은 번지부터 차례로 저장된다.

Performance

Performance는 컴파일러에 의해 결정된다.

컴파일러의 목표는 성능을 향상시키는 것으로, 결국 IC를 낮추고 CPI를 낮추는 것이다.

Common case를 single instruction으로 만들어서 IC를 낮춘다.

또한 $\times 2^i$를 <pre>sll $t0, $t0, i</pre>와 같이 변환하여 CPI를 낮춘다.

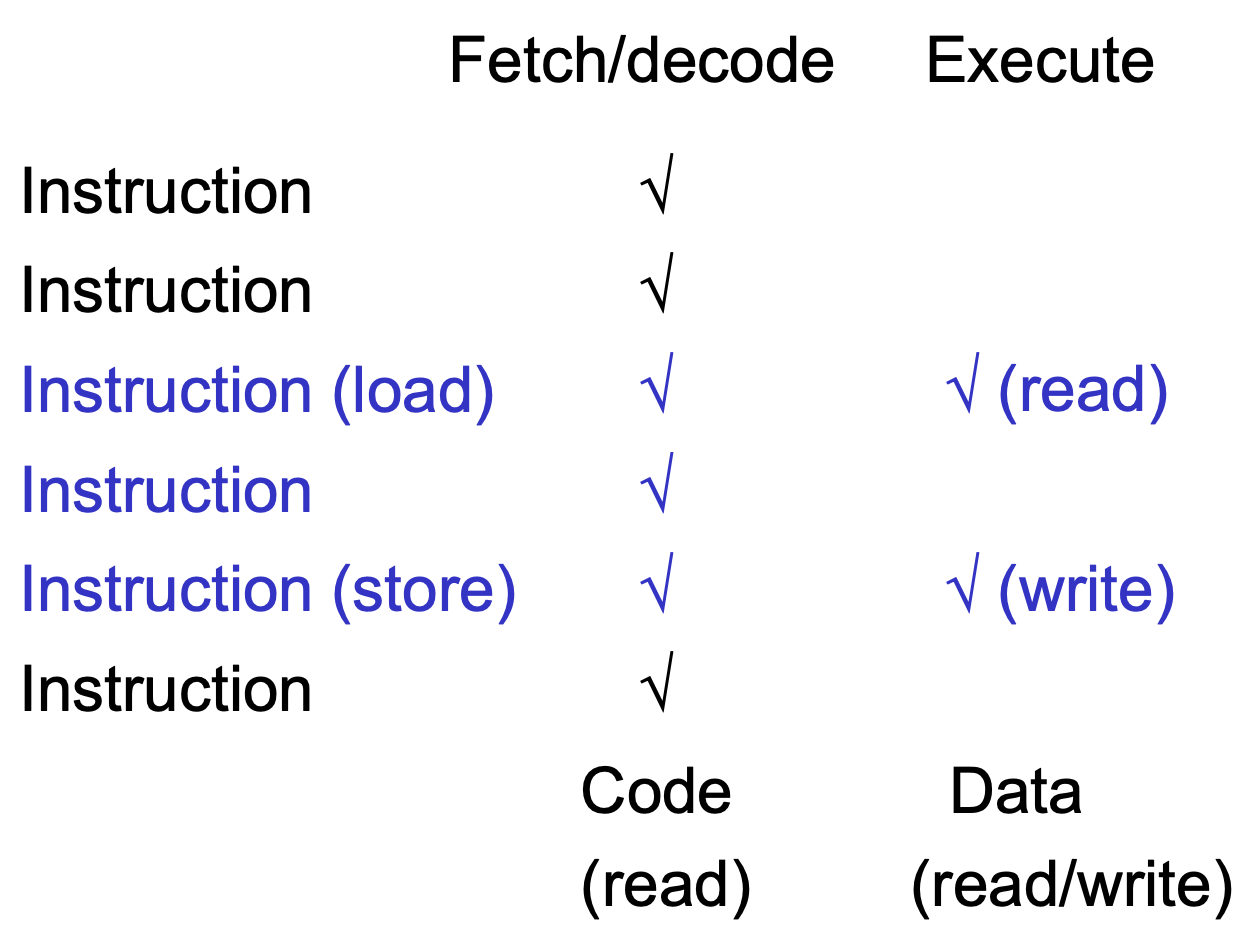

Instruction과 메모리 접근

모든 instruction들은 실행을 위해서는 fetch을 해야하기 때문에 반드시 메모리에 한번씩은 접근을 하게 된다.

Load/store는 메모리의 데이터를 읽거나 저장해야하기 때문에 execute 과정에서 추가적으로 메모리에 접근하게 된다.

fetch/decode 과정은 모두 memory read이다.

예시

<pre>

lw $t0, 32($s3)

add $t0, $s2, $t0

sw $t0, 48($32)

</pre>

위 코드에서 메모리에 접근하는 횟수는 총 5번이다.

= 각 instruction에서 fetch (3) + lw/sw에서 execute(2)

= memory read (4) + memory write (1)

Register Optimization

Register vs. Memory

레지스터는 프로세서 안에 존재하기 때문에, 레지스터에 접근하는 것이 메모리에 접근하는 것보다 훨씬 속도가 빠르다.

또한 메모리에 접근하기 위해서는 load/store을 사용해야 한다.

따라서 메모리에 접근하는 operating이 늘어나면 IC가 증가하게 된다.

Register Optimization

= Register allocation + register spill

메모리에 접근하는 것을 줄이고, 레지스터를 효율적으로 사용하기 위해서는 register optimization이 중요하다.

Register optimiaztion은 일반적으로 컴파일러가 결정한다.

만약 assembly programming이라면 assembly programmer가 결정한다.

Register Allocation

Register allocation이란 어떤 데이터가 어떤 레지스터에 저장될 것인가를 결정하는 것이다.

레지스터를 사용하기 위해서는 어떤 데이터가 어떤 레지스터에 저장될 것인가를 결정해야 한다.

Register Spill

Register spill이란 덜 사용되는 변수의 레지스터를 메모리에 저장해서 레지스터를 비우는 것이다.

프로그램이 많은 변수를 사용한다면 32개의 레지스터가 부족할 수도 있다.

이를 위해서 register spill을 한다

Constant Zero

MIPS는 register 0($zero)가 항상 0의 값을 가진다.

여기에는 값을 저장하거나 변경할 수 없다.

비록 하나의 레지스터를 사용하지는 못하지만 아래의 instruction들을 구현하지 않게 됨으로써의 장점이 더 크다.

- 레지스터 간 데이터 move

- 대체 : <pre>add $t2, $s1, $zero</pre>

- clear register

- 대체 : <pre>add $t2, $zero, $zero</pre>

- jump if eaual zero (beqz)

- 대체 : <pre>beq $t2, $zero, destination</pre>

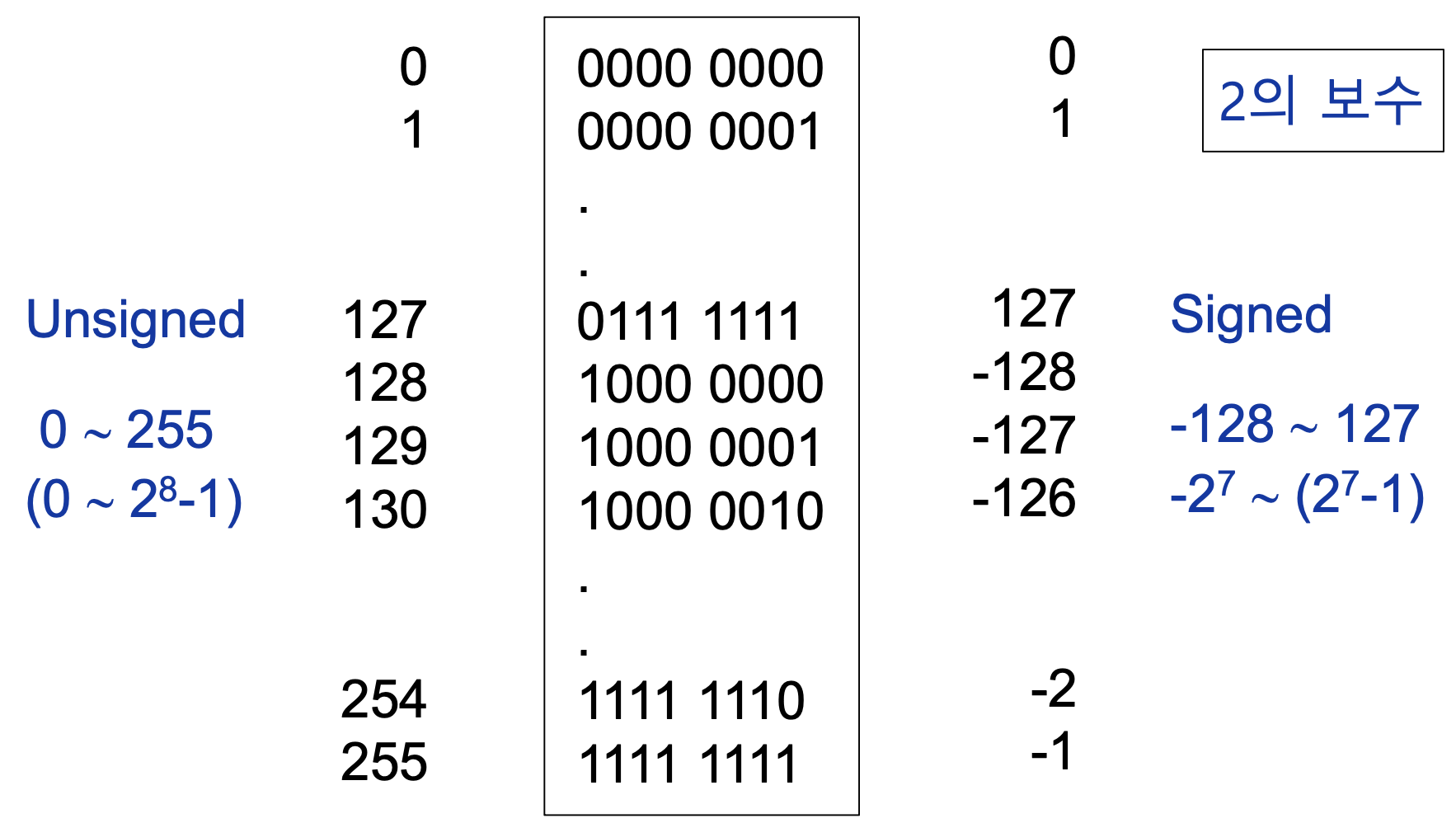

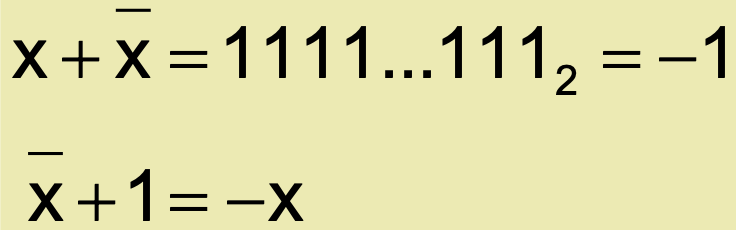

음수 표현 : 2's Complement

Negative integer는 2's complement를 사용한다.

2's complement는 1의 보수에서 +1을 한 것이다.

2's Complement

1byte에서 unsigned number는 0~255($2^8-1$)까지 표현이 가능하다.

1byte에서 signed number는 -128~127($2^7 - 1$)까지 표현이 가능하다.

Signed일 때 1000 0000이 -128을 나타내기 때문에 음의 방향으로 하나의 수를 더 표현 가능한 것이다.

32bit에서 2's Complement

32bit에서도 맨 앞의 bit 1개를 sign으로 표현한다.

따라서 $-2^{31} \, ~ \, 2^{31} - 1$ 까지의 수를 표현할 수 있다.

즉, 음수 방향으로 하나의 수를 더 표현할 수 있다.

2's Complment를 사용하는 이유

1의 보수를 사용할 경우 원래 수와 보수를 더하면 0이 아닌 -1이 나온다.

이는 사칙연산을 할 때 추가적인 보정을 필요로 한다.

예를 들어

$+2 = 0000 \; 0000 \; .... \; 0010_2$

$-2 = 1111 \; 1111 \; .... \; 1101_2$ (1's complement)

을 더할 경우 -1이 나온다.

이는 2의 보수를 이용하면 해결된다.

2의 보수는 1의 보수에 1을 더한 것이기 때문에 원래 수와 2의 보수를 더하면 0이 나온다.

따라서 2의 보수를 이용하는 것이 ALU를 만들기 편하다.

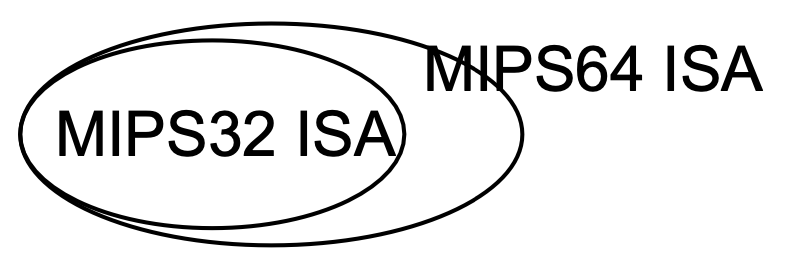

64-bit MIPS ISA

64bit에서도 MIPS의 insturction은 32bit이다.

또한 32-bit와 마찬가지로 I, R, J format을 사용한다.

이는 기존의 32bit MIPS와 compatibility을 위해서 그대로 지원해야 하기 때문이다.

대신 2개의 instruction을 한번에 fetch함으로써 성능을 크게 향상시킨다.

Assembly Language v.s. Machine Language

Assembly language는 machine language(binary language)을 사람이 인지하기 쉽기 위해 만든 것으로 mnemonic이다.

따라서 assembly와 machine code는 추상화 레벨이 같다.

다만 둘의 표현 방식은 다르다.

Assembly code에서는 destination first이지만, machine code에서는 destination보다 source가 앞서 온다.

- Assembly language

- destination first

- 예 : add a, b, c => a = b+c

- Machine language

- source first

- 예 : add b, c, a => a = b + c

Pseudoinstruction

Pseudoinstruction은 figments of assembler's imagination이다.

Assembly는 pseudoinstruction을 제공한다.

MIPS에서 실제로 지원하지는 않지만 프로그래머가 익숙하기에 가상의 instruction을 제공하는 것이다.

대부분의 assembler instruction은 machine instruction으로 1:1 변환된다.

그러나 하나의 pseudoinstruction은 여러 machine instruction으로 변환되는 경우가 있기 때문에 performance는 machine instruction을 카운트 해야 한다.

예시 1

<pre>move $t0, $t1</pre>는 MIPS가 실제 제공하는 instruction이 아니지만, assembly는 이를 지원한다.

실제 컴파일 결과는 <pre>add $t0, $t1, $zero</pre>와 같이 변환된다.

예시 2

<pre>blt $t0, $t1, 4</pre>

blt는 pesudoinstruction으로, branch less than을 의미한다.

이는 machine code에서 slt + bne로, 다음과 같은 machine code로 변환된다.

<pre>

slt $at, $t0, $t1 // if $t0 < $t1 -> $at = 1

bne $at, $zero, 4 // if $at != 0 -> jump to 4

....

</pre>

$at는 register 1로, assembler temporary를 나타낸다.

'Computer Science > Computer Architecture' 카테고리의 다른 글

| 2. MIPS : ALU and Data Transfer Instruction (0) | 2021.04.17 |

|---|---|

| 2. MIPS : Instruction Format & Addressing Mode (0) | 2021.04.17 |

| 1. Multicore (0) | 2021.04.10 |

| 1. Good ISA (0) | 2021.04.10 |

| 1. 컴퓨터 성능 개선/결정 (How to improve) (0) | 2021.04.03 |

댓글